Bæði SoC (System on Chip) og SiP (System in Package) eru mikilvægir áfangar í þróun nútíma samþættra hringrása, sem gera kleift að smækka, auka skilvirkni og samþættingu rafeindakerfa.

1. Skilgreiningar og grunnhugtök SoC og SiP

SoC (System on Chip) - Samþætting alls kerfisins í einn örgjörva

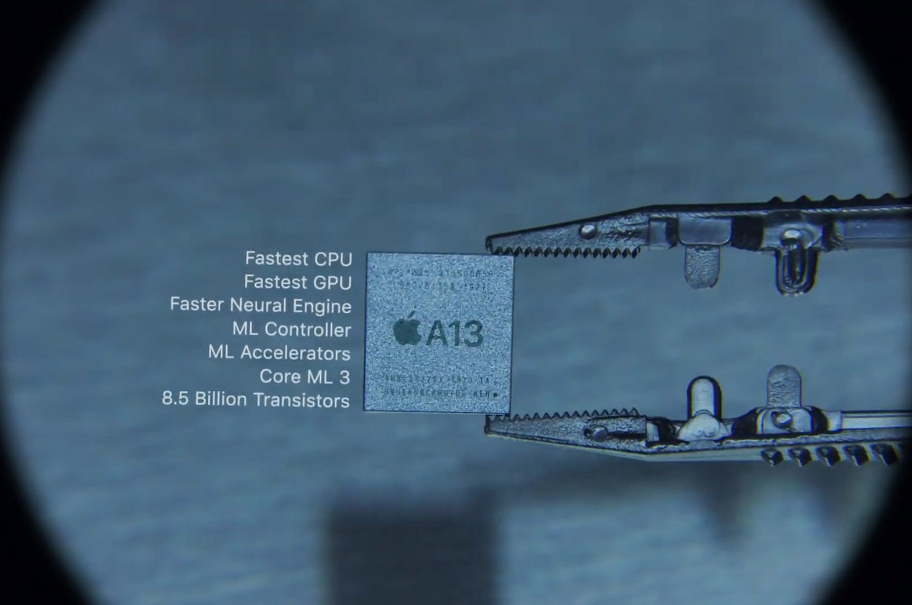

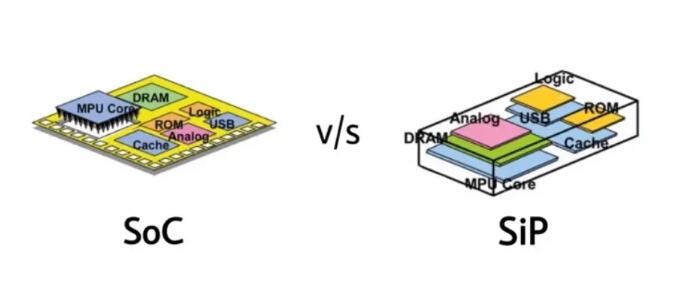

SoC er eins og skýjakljúfur þar sem allar virknieiningar eru hannaðar og samþættar í sama efnislega örgjörvann. Meginhugmyndin á bak við SoC er að samþætta alla kjarnaíhluti rafeindakerfis, þar á meðal örgjörvann (CPU), minni, samskiptaeiningar, hliðrænar rásir, skynjaraviðmót og ýmsar aðrar virknieiningar, í einn örgjörva. Kostir SoC liggja í mikilli samþættingu og smæð, sem veitir verulegan ávinning í afköstum, orkunotkun og stærð, sem gerir hann sérstaklega hentugan fyrir afkastamiklar, orkunæmar vörur. Örgjörvarnir í Apple snjallsímum eru dæmi um SoC örgjörva.

Til dæmis er SoC eins og „ofurbygging“ í borg þar sem allar aðgerðir eru hannaðar innan hennar og ýmsar virkniseiningar eru eins og mismunandi hæðir: sumar eru skrifstofurými (örgjörvar), sumar eru afþreyingarrými (minni) og sumar eru samskiptanet (samskiptaviðmót), allt saman safnað saman í sömu byggingunni (flís). Þetta gerir öllu kerfinu kleift að starfa á einni kísilflís, sem nær meiri skilvirkni og afköstum.

SiP (kerfi í pakka) - Sameining mismunandi örgjörva

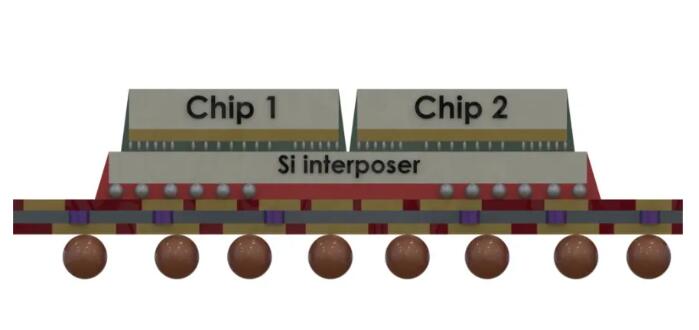

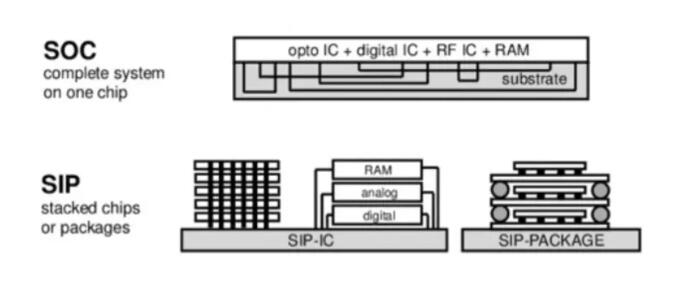

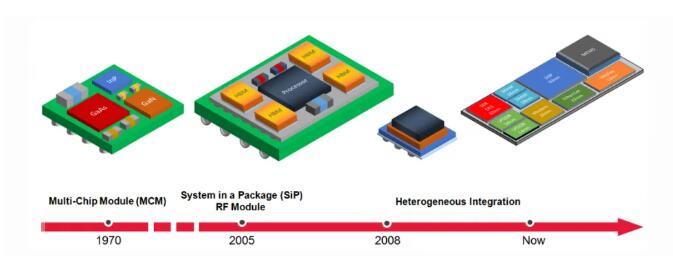

Aðferðin við SiP-tækni er önnur. Hún er frekar eins og að pakka mörgum örgjörvum með mismunandi virkni innan sömu efnislegu umbúða. Hún leggur áherslu á að sameina marga virkniörgjörva með umbúðatækni frekar en að samþætta þá í einn örgjörva eins og SoC. SiP gerir kleift að pakka mörgum örgjörvum (örgjörvum, minni, RF-örgjörvum o.s.frv.) hlið við hlið eða stafla þeim innan sömu einingar og mynda þannig lausn á kerfisstigi.

Hugmyndina á bak við SiP má líkja við að setja saman verkfærakassa. Verkfærakistan getur innihaldið mismunandi verkfæri, svo sem skrúfjárn, hamar og borvélar. Þótt þetta séu sjálfstæð verkfæri eru þau öll sameinuð í einum kassa til að auðvelda notkun. Kosturinn við þessa aðferð er að hægt er að þróa og framleiða hvert verkfæri sérstaklega og „setja þau saman“ í kerfispakka eftir þörfum, sem veitir sveigjanleika og hraða.

2. Tæknilegir eiginleikar og munur á SoC og SiP

Mismunur á samþættingaraðferðum:

SoC: Mismunandi virknieiningar (eins og örgjörvi, minni, inntak/úttak o.s.frv.) eru hannaðar beint á sama kísilflís. Allar einingar deila sömu undirliggjandi ferli og hönnunarrökfræði og mynda þannig samþætt kerfi.

SiP: Hægt er að framleiða mismunandi virkniflögur með mismunandi ferlum og sameina þær síðan í eina umbúðaeiningu með þrívíddarumbúðatækni til að mynda efnislegt kerfi.

Flækjustig og sveigjanleiki hönnunar:

SoC: Þar sem allar einingar eru samþættar á einni flís er hönnunarflækjustigið mjög hátt, sérstaklega fyrir samvinnuhönnun mismunandi eininga eins og stafrænna, hliðrænna, RF og minnis. Þetta krefst þess að verkfræðingar hafi djúpa hönnunarhæfni yfir svið. Ennfremur, ef hönnunarvandamál koma upp með einhverja einingu í SoC, gæti þurft að endurhanna alla flísina, sem hefur í för með sér verulega áhættu.

SiP: Aftur á móti býður SiP upp á meiri sveigjanleika í hönnun. Hægt er að hanna og staðfesta mismunandi virknieiningar sérstaklega áður en þær eru pakkaðar inn í kerfi. Ef vandamál koma upp með einingu þarf aðeins að skipta um þá einingu og aðrir hlutar verða óbreyttir. Þetta gerir einnig kleift að þróa hraðari og minnka áhættu samanborið við SoC.

Samrýmanleiki ferla og áskoranir:

SoC: Samþætting mismunandi aðgerða eins og stafrænna, hliðrænna og RF-tengdra kerfa á einn örgjörva stendur frammi fyrir verulegum áskorunum í samhæfni ferla. Mismunandi virknieiningar krefjast mismunandi framleiðsluferla; til dæmis þurfa stafrænar rásir hraðvirk og orkusparandi ferli, en hliðrænar rásir geta þurft nákvæmari spennustýringu. Það er afar erfitt að ná samhæfni milli þessara mismunandi ferla á sama örgjörva.

SiP: Með pökkunartækni getur SiP samþætt flísar sem framleiddar eru með mismunandi ferlum og leyst þannig vandamál sem tengjast samhæfni ferla sem SoC-tækni stendur frammi fyrir. SiP gerir kleift að vinna saman margar ólíkar flísar í sama pakkanum, en nákvæmniskröfurnar fyrir pökkunartækni eru miklar.

Rannsóknar- og þróunarferli og kostnaður:

SoC: Þar sem SoC krefst þess að allar einingar séu hannaðar og staðfestar frá grunni, er hönnunarferlið lengra. Hver eining verður að gangast undir stranga hönnun, staðfestingu og prófanir, og heildarþróunarferlið getur tekið nokkur ár, sem leiðir til mikils kostnaðar. Hins vegar, þegar fjöldaframleiðsla er komin í gang, er einingarkostnaðurinn lægri vegna mikillar samþættingar.

SiP: Rannsóknar- og þróunarferlið er styttra fyrir SiP. Þar sem SiP notar beint núverandi, staðfesta virkni flísar fyrir umbúðir, dregur það úr þeim tíma sem þarf til að endurhanna einingar. Þetta gerir kleift að flýta fyrir vörukynningum og lækkar rannsóknar- og þróunarkostnað verulega.

Kerfisafköst og stærð:

SoC: Þar sem allar einingar eru á sama örgjörvanum eru samskiptatöf, orkutap og truflanir á merkjum lágmarkaðar, sem gefur SoC einstakan kost í afköstum og orkunotkun. Stærð þess er lítil, sem gerir það sérstaklega hentugt fyrir forrit með mikla afköst og orkuþörf, svo sem snjallsíma og myndvinnsluflögur.

SiP: Þó að samþættingarstig SiP sé ekki eins hátt og hjá SoC, getur það samt sem áður pakkað mismunandi örgjörvum saman á þéttan hátt með því að nota fjöllaga pökkunartækni, sem leiðir til minni stærðar samanborið við hefðbundnar fjölflögulausnir. Þar að auki, þar sem einingarnar eru líkamlega pakkaðar frekar en samþættar á sama kísilflísinn, getur það samt sem áður uppfyllt þarfir flestra forrita, þótt afköstin séu ekki eins og hjá SoC.

3. Umsóknarsviðsmyndir fyrir SoC og SiP

Umsóknarsviðsmyndir fyrir SoC:

SoC hentar yfirleitt fyrir svið þar sem miklar kröfur eru gerðar um stærð, orkunotkun og afköst. Til dæmis:

Snjallsímar: Örgjörvarnir í snjallsímum (eins og A-serían frá Apple eða Snapdragon frá Qualcomm) eru yfirleitt mjög samþættar SoC-örgjörvar sem innihalda örgjörva, skjákort, gervigreindarvinnslueiningar, samskiptaeiningar o.s.frv., sem krefjast bæði öflugrar afköstar og lágrar orkunotkunar.

Myndvinnsla: Í stafrænum myndavélum og drónum þurfa myndvinnslueiningar oft sterka samsíða vinnslugetu og lága seinkun, sem SoC getur náð á skilvirkan hátt.

Afkastamikil innbyggð kerfi: SoC hentar sérstaklega vel fyrir lítil tæki með strangar kröfur um orkunýtingu, svo sem IoT tæki og klæðanleg tæki.

Umsóknarsviðsmyndir fyrir SiP:

SiP býður upp á fjölbreyttari notkunarmöguleika, sem hentar fyrir svið sem krefjast hraðrar þróunar og fjölþættrar samþættingar, svo sem:

Samskiptabúnaður: Fyrir grunnstöðvar, beinar o.s.frv. getur SiP samþætt marga RF og stafræna merkjavinnsluaðila, sem flýtir fyrir vöruþróunarferlinu.

Neytendavörur: Fyrir vörur eins og snjallúr og Bluetooth heyrnartól, sem hafa hraðar uppfærslur, gerir SiP tækni kleift að hraða kynningu á nýjum vörum.

Rafmagnstæki í bílum: Stjórneiningar og ratsjárkerfi í bílakerfum geta nýtt sér SiP-tækni til að samþætta fljótt mismunandi virknieiningar.

4. Framtíðarþróun SoC og SiP

Þróun í SoC þróun:

SoC mun halda áfram að þróast í átt að meiri samþættingu og ólíkri samþættingu, hugsanlega með því að fela í sér meiri samþættingu gervigreindarörgjörva, 5G samskiptaeininga og annarra virkni, sem knýr áfram frekari þróun greindra tækja.

Þróun SiP:

SiP mun í auknum mæli treysta á háþróaða umbúðatækni, svo sem framfarir í 2,5D og 3D umbúðum, til að pakka örgjörvum með mismunandi ferlum og virkni þétt saman til að mæta ört breytilegum kröfum markaðarins.

5. Niðurstaða

SoC er frekar eins og að byggja fjölnota risastóran skýjakljúf, þar sem allar virknieiningar eru safnaðar saman í einni hönnun, sem hentar fyrir forrit með afar miklar kröfur um afköst, stærð og orkunotkun. SiP, hins vegar, er eins og að „pakka“ mismunandi virkniflögum inn í kerfi, með meiri áherslu á sveigjanleika og hraða þróun, sérstaklega hentugt fyrir neytendatækni sem þarfnast skjótra uppfærslna. Báðir hafa sína kosti: SoC leggur áherslu á bestu kerfisafköst og stærðarhagkvæmni, en SiP leggur áherslu á sveigjanleika kerfisins og hagræðingu þróunarferlisins.

Birtingartími: 28. október 2024